PI Name & Affiliation:

Dr.K. Sivasankaran,

Associate Professor,

School of Electronics Engineering (SENSE),

Vellore Institute of Technology, India

Collaborator Affiliation:

Dr. Atabek Atamuratov,

Urgench State University, Urganch,

Uzebekistan

Funding Agency: DST

Scheme: International Bilateral Co-operation

Overlay: Rs. 17,89,200

Duration of the Project: 3 Years

Dr.K. Sivasankaran

Associate Professor

Dr. Atabek Atamuratov

Project Description

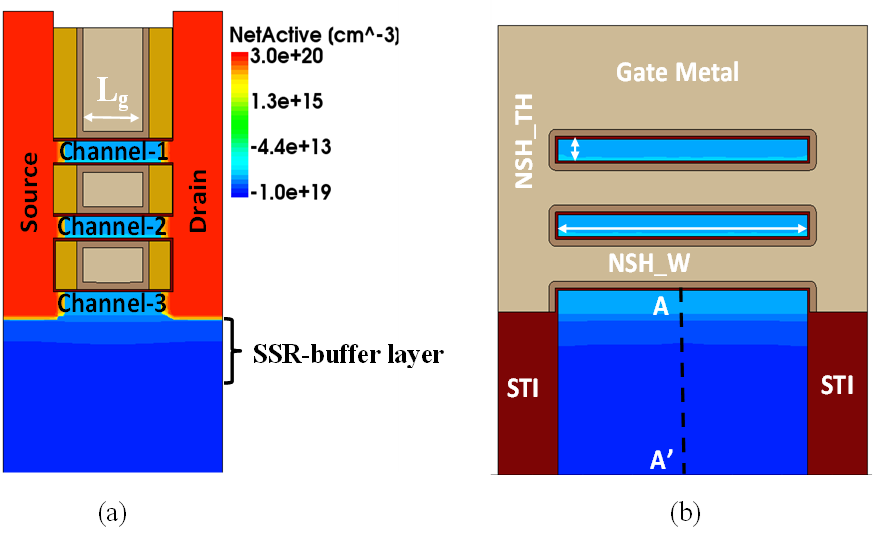

In advanced non-planar MOSFETs architecture, the reliability issue is the primary concern for the device engineers due to aggravated local self-heating arising from the enhanced active power dissipation inside the device structure. Recently, stacked nanosheet field effect transistor (SNSHFET) is firmly believed to be the successor of FinFETs at 7 nm technology and beyond due to its superior leakage control and high current density than FinFETs. The objective of this research proposal is to design Sub 7nm stacked nano sheet field effect transistor immune to self-heating and to model thermal resistances and capacitances using small-signal ac parameters. The other objective is to study the parametric variation of self-heating effect (SHE) in SNSHFET for different substrate, gate length (LGate), nanosheet width (NSH_W) and nanosheet thickness (NSH_T). Finally, impact of self-heating on reliability of the device such as Bias Temperature Instability (BTI), Hot Carrier Injection (HCI), and Time Dependent Dielectric Breakdown (TDDB) will be investigated.